2021.03.29

FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(4) ASIC屋が疑問に感じる「FPGAにおけるPLLの同期設計は?」

#FPGA #ASIC #LSI #クロック #スキュー #座談会

トップ > 技術ナレッジのアーカイブ > FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界 > FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(4) ASIC屋が疑問に感じる「FPGAにおけるPLLの同期設計は?」

2021.03.29

#FPGA #ASIC #LSI #クロック #スキュー #座談会

1987年よりLSIに携わる。入社後、論理シミュレーションし試作品の作成、LSIのテスターで電気的特性の評価といった一連の業務を担当。その後タイミング設計と論理設計を15〜20年間従事する。

当初はgate arrayだったが、その後特定用途向けのASICの開発、論理設計だけでなくお客様との折衝も担当し30年ほど関わる。

半導体メーカーにてLSI設計開発

主にキャッシュディスペンサー・自動改札機・航空券発券機・PCのCD-RAMドライブ などの製品に関わる。

2000年10月 テクノプロ・デザイン社に入社

・自動車向け、エンジン制御・エアバッグ Etc マイコン設計開発

・ディスプレイ搭載回路基板設計開発、FPGA設計に従事。

仕様設計-詳細設計-試作-量産まで携わる。

また、現地中国人(上海)設計者指導、教育、アドバイザーまで様々なプロジェクトに関わる。

・2017年4月 CDA(キャリアデザインアドバイザー)着任

支店技術部組織構築補助、技術社員(エンジニア)のスキルアップ支援

株式会社テクノプロ テクノプロ・デザイン社

1997年 株式会社テクノプロ テクノプロ・デザイン社に新卒入社

人工衛星回路設計・ECU装置設計など約20年経験

現在、採用部門部長

坂野 ー

ASICはそこまできちんと考えて設計しないといけないのですが、 以前、FPGA独特な設計手法を使ってASICのようにシビアな状況で動作させようとしたことがあります。

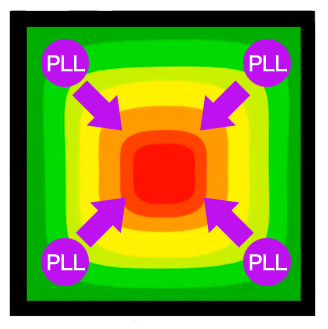

FPGAは以下のようにクロック生成回路(PLL)が存在しています。

PLLの役目としては、外から入っきたクロックをPLLに入れ、クロックを2倍にしたり、半分にしたり、位相をずらして立ち上がりではなく立ち下がりにするとか、こういう動きをして内部にクロックを供給する役目があります。

PLLで配置すると、様々なPLLが適切にクロックを調整してタイミング設計の中で自動で行ってくれます。

LSIによってはPLLが四隅にない場合、反対側にクロックラインを通さなければいけないから、FPGAでは設計不可能です。

ですのでFPGAは四隅にPLLがあります。

坂野 ー

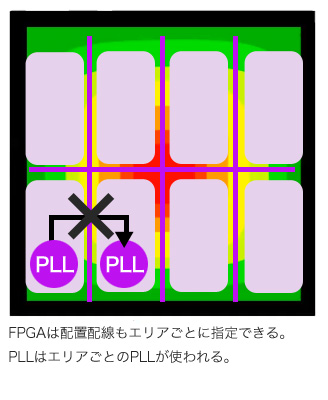

FPGAの場合、配置配線もエリアごとに指定できるので、機能やブロックごとに切り分けます。

例えばエリアを区切り、その区切りの範囲内で使われるPLLは絶対限られたものになります。

なぜならメッシュ配線されていているから。

他のエリアで跨いでPLLが使われることはなく、エリアごとのPLLが使われます。

北原 ー 回路ブロックの配置は誰が決めるのですか?

坂野 ー 設計者が決めます。配置配線するときに自動も可能ですし、ユーザー指定で自由に配置することもできます。左上のPLLと右下のPLLが同時に動くような同期回路はなく、処理が終わった後の回路のデータが別の機能のエリアで叩かれる、ということはあるかなと思います。

髙島 ー 非同期設計ですね。それならわかります。

坂野 ー

同期回路としてはそういう設計はしないようにしています。

ただ注意しなければならないのは、ASICエンジニアが考える緻密な回路にするとFPGAではまともに動かないことがあります。もしくは製品スペックを満たさないとか。

髙島 ー FPGA使って実機デバックするという用途なら「動けば良い」でいいけど、いろんなユーザーの手に渡る「量産」となると、一定の範囲でしっかり動作するものを供給しないと量産に耐えられないと、そこが気になりましたね。

坂野 ー 先ほど述べた「エリア指定」というのは通常であればまずやりません。でもどうにかしてやらないと、という場面ではメーカーに問い合わせたり。

誤解を招くような表現があったので補足です。

本稿での議論は4つのPLLを想定した場合の物理的な距離によるスキューを問題とし、

小さいエリアに分けて、エリア毎のPLLを使用する手法について紹介しています。

一方で1つのPLLで設計した場合、チップ全体のLE(ロジックエレメント)

を使うことになり、チップ中心の電圧ドロップなどバラツキ要因を考慮した自動配置配線がツールで行われるのが一般的です。