2021.03.29

FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(1) ASIC屋が「FPGAって仕様情報だけで設計できるのか?」と感じるFPGAの品質管理

#FPGA #ASIC #LSI #クロック #スキュー #座談会

トップ > 技術ナレッジのアーカイブ > FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(1) ASIC屋が「FPGAって仕様情報だけで設計できるのか?」と感じるFPGAの品質管理

2021.03.29

#FPGA #ASIC #LSI #クロック #スキュー #座談会

時代の変化とともに、FPGAが製品に広範囲の製品で使われるようになり、関わるエンジニアも増えてきました。

一方、FPGAと「対(つい)」で語られることの多いASIC。FPGAとは用途やニーズも異なり、その差を製品レベルで論じられることは多いのですが、エンジニア視点、つまり、制作工程の違いを語られることは少ないと思います。

今回は現場のエンジニアはどのように両者を捉えているのか?二人のエンジニアに伺いました。

1987年よりLSIに携わる。入社後、論理シミュレーションし試作品の作成、LSIのテスターで電気的特性の評価といった一連の業務を担当。その後タイミング設計と論理設計を15〜20年間従事する。

当初はgate arrayだったが、その後特定用途向けのASICの開発、論理設計だけでなくお客様との折衝も担当し30年ほど関わる。

半導体メーカーにてLSI設計開発

主にキャッシュディスペンサー・自動改札機・航空券発券機・PCのCD-RAMドライブなどの製品に関わる。

2000年10月 テクノプロ・デザイン社に入社

・自動車向け、エンジン制御・エアバッグ Etc マイコン設計開発

・ディスプレイ搭載回路基板設計開発、FPGA設計に従事。

仕様設計-詳細設計-試作-量産まで携わる。

また、現地中国人(上海)設計者指導、教育、アドバイザーまで様々なプロジェクトに関わる。

・2017年4月 CDA(キャリアデザインアドバイザー)着任

支店技術部組織構築補助、技術社員(エンジニア)のスキルアップ支援

株式会社テクノプロ テクノプロ・デザイン社

1997年 株式会社テクノプロ テクノプロ・デザイン社に新卒入社

人工衛星回路設計・ECU装置設計など約20年経験

現在、採用部門部長

北原 ー FPGAは、評価用として設定を様々に変えて使い回す、というイメージがありましたが、量産をやっていくときに壁はありましたか?

髙島 ー

FPGAを量産していくことに、(正確には知らないですが)弊害があるのではないかと

感じています。

タイミング解析をするためには、プロセスばらつきや電源電圧、動作温度の条件が必要になりますが、そのなかでFPGAはどうやってプロセスパラメータを入手するのかということが疑問に思っています。

坂野 ー

そもそもFPGAは「最初からできあがったもの」という概念です。

つまりFPGAの内部で動作する周波数や、温度、電源電圧は、仕様として各製品ごと定められていて、ばらつきも考慮されて作られています。

その範囲内で使用するべきですが、実際に使うにあたって、仕様通りに使って論理設計をしたら、そのまま動くかというと、もちろん物理的な回路を組み込んでいくので、まともには動かない場合もあります。

北原 ー 例えば、立ち上がり/立ち下がり時間が+ー1%〜2%ずれることもあると思うのですが、そのズレってシビアなんですか?

坂野 ー シビアではありますが、 Xilinx(ザイリンクス)社、アルテラ社(現在はインテルのFPGA部門)にはFPGAの開発ソフトウェアがありまして、アルテラ社ならQuartusというのがあり、一通り中に書き込むまでの一連のことができますね。

北原 ー それは温度範囲も考慮して、バッと書き込んでくれる?

坂野 ー 仕様条件を入力する必要があります。使用環境-30℃、+-0.1ボルトの電源電圧のブレとか。それらを入力すると、動作する回路、しない回路のリストが出てきます。

北原 ー HDL設計したポイントごとに「ここが動く、動かない」がわかるわけですか。

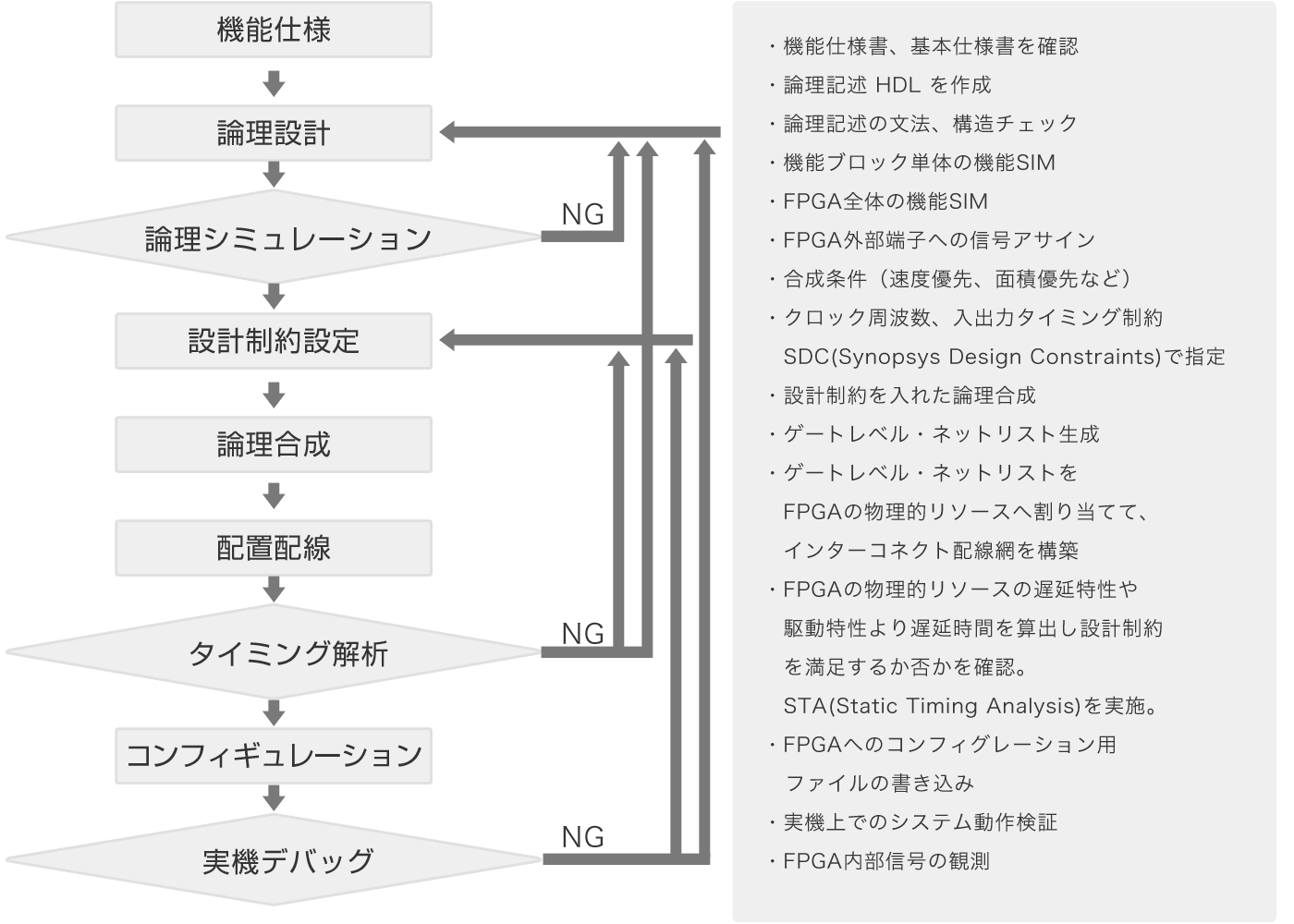

これによると HDL記述から論理回路に落とす時に論理合成を行い、次に配置配線、そしてタイミング解析を行う、こういう流れなのですが、先ほどの電圧とか温度の条件で回路が動作するかどうかの判断は、この工程でいうと論理シミュレーションのことですか?

坂野 ー

いえ、配置配線とタイミング解析の間ですね。

タイミング解析ツールというのがありまして、それを実行することで条件に合わない箇所を見つけることができます。(采女注:タイミング解析ツール、というのは前述の開発ソフトウェアとは違うもの?それとも同じもの?)

なぜかというと、その前に「配置配線」がすでにシミュレーター上で行われていて「FPGAのこの部分にこの回路を置く」といったことが物理的にできているからです。

北原 ー ASICのHDL設計では、タイミング解析ツールというものはないのですか?

髙島 ー

あります。

配置配線の後、論理シミュレーションはASICでも行います。SPEF(エスぺフ)というフォーマットのファイルを使ってタイミング解析を行います。さらに、SPEFを使って配置配線後の論理シミュレーションも行っています。

髙島 ー そこで一つの疑問があります。

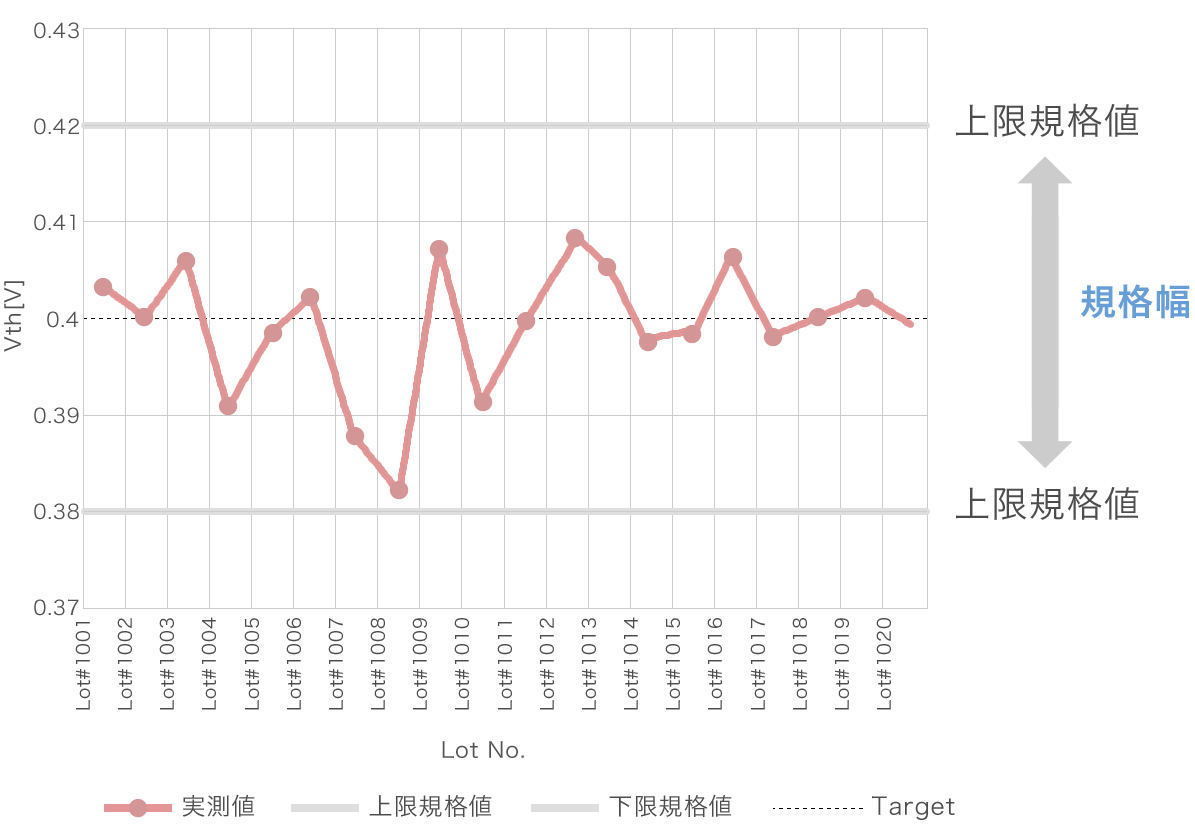

FPGAではVth設計管理幅の情報をいかに入手して設計に反映させるか、ということです。

工程能力指数というのがあって、vthを0.4に置いても、上が0.41、下が0.38になったり。 分布図でいうと

平均的に多いのはターゲットの0.4ですが、それでもばらつきがあります。

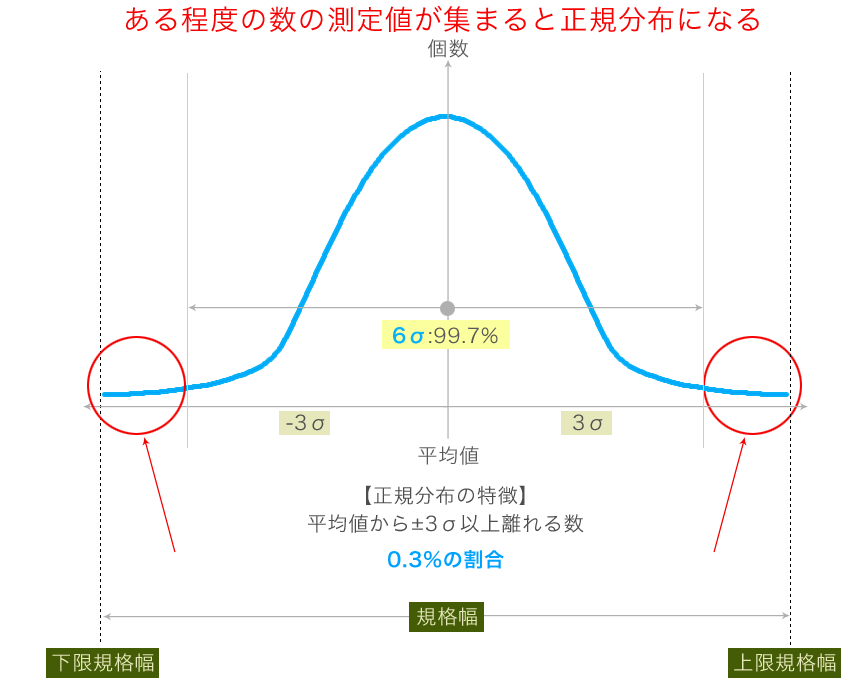

大きさによって、個数が減っていき、ある程度の数の測定値が集まると上図のような正規分布になります。

この図で示したように製造する上でばらつき(プロセスばらつき)というのは多かれ少なかれあります。

同じ半導体チップ内においてもばらつきがあります。

そして、ばらつきとしては、電源ばらつき、温度ばらつきがあります。

電源電圧のIRドロップによる電圧ばらつきが同じチップ上においてもあります。

チップ内で常に動作するクロックや、あまり動かないDC的な信号もあり、

チップ内で部分的に消費電力も変わり、部分的に温度も変わっています(温度ばらつき)。

FPGAにおいて、ユーザーの論理情報を入れると配置配線の物理的な距離によって、タイミング的に厳しい状況になることがありますが、

セットアップやホールドが満たせない状態になることがあります。(ASICでも同様です)。

そうするとデータラインの遅延を小さくする等、何らかのタイミングを満たすような対策を打たなければなりません。

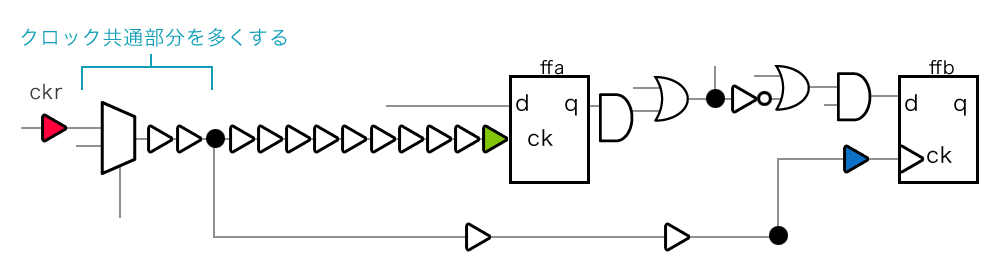

そもそもクロックタイミングというのは上図の出し側のffと受け側のffのデータ、そして出し側のクロックと受け側のクロックがばらついていたらどうしようもなく、セットアップ、ホールドが満たせません。

そうすると、データラインの対策だけでは無理で、クロックラインもスキューが合うように制御が必要になります。

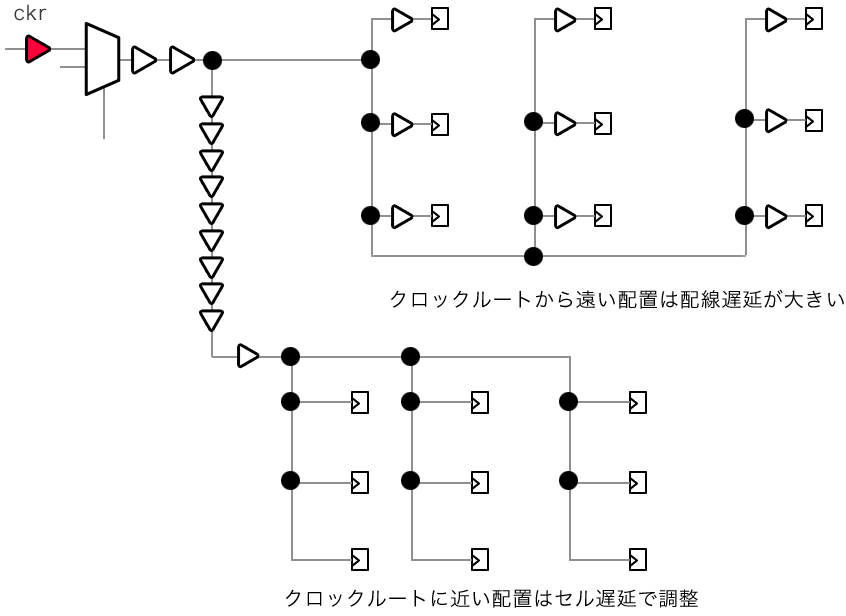

そのための方法としてASICの場合、「クロックツリー」でクロックのスキューを最小にするための調整をし、それぞれがffの到達するクロックにディレイがない状態にします。

例えば上図はFFの配置イメージですが、クロックルートから近いところに固まってるFF群と、遠い、しかもそれぞれが離れているとなると、そこを調整する時に配線遅延まで含んだセル遅延で何とか補って調整します。

また、IRドロップという状態があって、チップ内の動作や電源配線の状況により、チップ内に電源電圧のドロップが発生します。

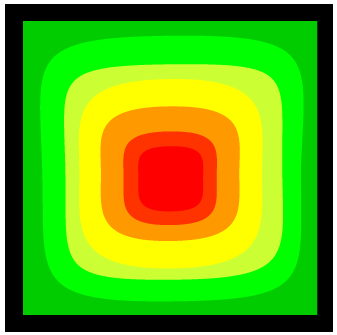

上図ではIRドロップの度合いを色で表現したものですが、小→中→大:緑→黄→赤とセンターにいくほどドロップの度合いが大きくなります。

問題は、チップの中に行けばいくほど電圧のドロップが大きくなりますが、さきほどのFFとクロックの関係が実際どこにあるのかがわかりません。

上図ドロップ図からもわかるように、電圧やプロセスのばらつきがチップ内色々なところに存在します。

これらのばらつきを無視して、クロックのスキューを合わせると、下図の「チップ内ばらつき考慮無し」の図のようになりますが、実際にはばらつきを考慮する必要があるので、

「Setupチップ内ばらつき考慮有り」の図のようにして、Setup評価を行い、「Holdチップ内ばらつき考慮有り」の図のようにして、Hold評価を行う必要があります。

「Setupチップ内ばらつき※考慮有り」した場合、出し側のクロックとff間のデータの遅延を大きな係数倍に、そして受け側のクロックを小さな係数倍にし、わざと厳しい状況にします。

これでセットアップが満たせるかどうかという評価をします。

ホールド評価は係数倍の付け方を逆にします。

「Holdチップ内ばらつき※考慮有り」した場合、出し側のクロックとff間のデータの遅延を小さな係数倍に、そして受け側のクロックを大きな係数倍にし、わざと厳しい状況にします。

これでホールドが満たせるかどうかという評価をします。

その時に必要なものが、どのくらいプロセスがばらついているかという情報になります。

※「チップ内ばらつき」とは、電源ばらつき、温度ばらつき、プロセスばらつきがあります。

北原 ー つまりFPGAの各製品で公表されている仕様以外でわからないことがあり、その事に対してのタイミング設計って量産FPGAはどうやってるのか、ということですよね?

髙島 ー そうですね。仕様が公表されていることでユーザーが使いやすくなっている、というのはわかるのですが、 実際にタイミング検証を行う人が、そのFPGAのVthがどの範囲でプロセスばらつきがあるのか分からないと、検証ができないのはないかと思います。

坂野 ー

FPGAの物理的なプロセスでいうと、なるべくクロックがバラつかないようにメッシュ配線しています。

メッシュ配線とは、クロック自体を網目状にし、いつどの時でも同じタイミングで届かせるために、一本で枝分けさせると先ほどのクロックツリーのようにしなければならないですけど、FPGAの場合は最初からクロックは端から端まで網目状にし、同じ負荷でクロックを到達させようという物理構造になっています。

もしドライビリティが足りないところは、中間にドライバをいれて予め調整されています。

髙島 ー

網目になっているということは、昔聞いたことがありますが、やっぱり疑問が。

どんなクロックでも、同じ経路を辿るようにできているならスキューは合うかもしれないですが、

ホントにそうなるの?っていう疑問が…

坂野 ー

もちろん網目にしただけではダメで、例えば右上と真ん中とでは物理的にどうしても到達時間は違い、真ん中は届きづらく、PLLから網目になって均等に届くとしてもぴったりにはならない。

そのために中間にドライバを入れることで、スピードを加速させるんです。これでスキュー差を小さくすることが最初からできるようになっています。

それに対して「このポイントに回路を置こう」としたとき、同じようなタイミングで届くということが前提なので、スキューのためにデータが取れる取れないという事は起きにくいんです。

さらに内部でのクロックとデータでのセットアップ、ホールドについて最低必要な時間というものが各FPGAに設定されています。物によってはマニュアルにも記載があると思います。もしわからなければ、私ならメーカーに聞きますね。「どれぐらいまでにデータが来てればいいの」とか。

温度範囲や電源電圧の範囲など様々な条件で細かく聞きます。そしてちゃんと証明証をもらった上で設計を始めます。

タイミング設計をやる時、SDCファイルでタイミング制約を加えていくと思いますが、そこに網羅した定量的な数値を加えて、タイミング設計をして配置配線をします。